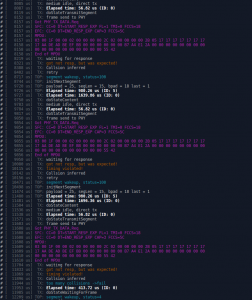

Für meine Masterarbeit beschäftige ich mich gerade mit Softcore-Prozessoren auf FPGAs. Dabei kommt für meine Arbeit der NEO430 zum Einsatz, ein sehr kleiner aber feiner Prozessor der an meinem Institut entwickelt wurde (von Stephan Nolting). Da ich aktuell noch nicht in einem Stadium bin, wo ich den Prozessor wirklich auf einem FPGA implementiere (auch wenn das der nächste Schritt ist) arbeite ich aktuell sehr viel mit Simulation, und da vor allem mit ModelSim. Ein bisschen was dazu hatte ich ja hier im Blog schon mal da zu geschrieben.

Nun hatte ich heute Abend die Idee, man könnte ja mal einen anderen Simulator ausprobieren. Mir hat es dabei GHDL angetan, vor allem, da er OpenSource ist, aber auch weil er einen interessanten Ansatz verfolgt: Der VHDL-Code wird mit einem umgebauten Compiler (GCC oder LLVM) direkt in Maschinencode kompiliert, und dieser Code dann ausgeführt. Dadurch soll der Simulator extrem schnell sein. Auf Windows ist das ganze etwas eingeschränkt, hier wird ein interner Codegenerator verwendet. Weiterlesen