Aktuell arbeite ich fleißig an meiner Masterabeit (einer der Gründe, warum es hier auf dem Blog so still ist…), und entwickele dafür auch ein paar Sachen in VHDL (ich entwickele also Hardware 🙂 ). Am Ende soll das ganze natürlich auf einem FPGA laufen (vielleicht sogar mal in einem echtem Chip, einem ASIC!), aber aktuell wird das ganze nur simuliert. Das ist zwar ziemlich langsam (aktuell etwa um den Faktor 1000), aber dafür kann man sich jedes Signal in seiner Schaltung ganz genau ansehen und bei Bedarf auch Debug-Ausgaben tätigen. Besonders das hat sich aktuell als sehr hilfreich dargestellt.

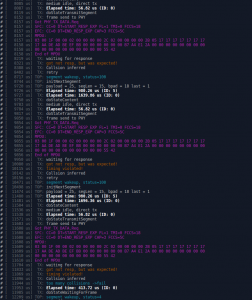

VHDL unterstützt das im Prinzip mit assert und report, allerdings finde ich die Ausgaben recht unübersichtlich, vor allem weil sie über mehr als eine Zeile gehen. Zudem ist alles einfarbig, so dass man schnell die Übersicht verliert. Ich habe mir als etwas überlegt, was etwas schöner aussieht (siehe Screenshot)

Dazu habe ich erst mal eine Funktion gebaut, welche die aktuell Zeit (seit dem Start der Simulation) in eckigen Klammern ausgibt, und danach den Inhalt einer line (was eine Art Pointer auf einen String ist). In VHDL ist das immer alles etwas komisch, aber so funktioniert es:

This file contains bidirectional Unicode text that may be interpreted or compiled differently than what appears below. To review, open the file in an editor that reveals hidden Unicode characters.

Learn more about bidirectional Unicode characters

| package body debug is | |

| procedure writelineOut(l: inout line) is | |

| variable tmp : line; | |

| begin | |

| write(tmp, ESC & "[2m["); | |

| write(tmp, now / 1 us * 1 us, UNIT => us, FIELD => 10); — round to 1us precision | |

| write(tmp, "] "& ESC & "[0m"); | |

| write(tmp, l.all); | |

| writeline(output, tmp); | |

| l := new string'(""); | |

| end procedure; | |

| end package body debug; | |

| –ausgabe: | |

| write(tmp2, ESC & "[2m" & PREFIX & ": " & ESC & "[0m"); | |

| write(tmp2, ESC & "[1mTracepoint "); | |

| write(tmp2, " (ID: " & integer'image(id) & ")" & ESC & "[0m"); | |

| writelineOut(tmp2); |

Herzstück des Ganzen ist die procedure writelineOut. Dort wird zunächst eine Zeile (tmp) zusammengebaut, und diese dann mit writeline ausgegeben. Dabei ist der erste Parameter die Datei, in die geschrieben werden soll, output ist hier eine vordefinierte Datei, die für die Standardausgabe steht. Um die Farben zu erzeugen werden Escape-Sequenzen verwendet, die aktuell Zeit wird aus der Variablen now extrahiert. Der Parameter UNIT sorgt dafür, dass die Zeit in Mikrosekunden ausgegeben wird, und FIELD dafür, das die Ausgabe immer 10 Zeichen breit ist (und rechtsbündig). Leider werden automatisch alle verfügbaren Nachkommastellen mit ausgeben, und ich habe keine Funktion gefunden, um wenigstens dafür zu sorgen, dass immer gleich viele ausgegeben werden (Nullen werden weggelassen), dadurch sah das ganze sehr unübersichtlich aus. Durch das Konstrukt now / 1us * 1us wird die Zeit auf 1 µs gerundet.

Wie die Ausgabe funktioniert sieht man weiter unten, dabei ist tmp2 auch wieder eine Variable vom Typ line. Auch hier wird wieder eine farbige Ausgabe benutzt. Variablenwerte kann man mit integer’image(x) in einen String konvertieren.

Wenn man diese Debugausgaben kräftig einsetzt, bekommen man auch eine so schöne Übersicht wie auf dem Screenshot. Das hat sich als sehr hilfreich rausgestellt 🙂 Übrigens funktionieren die farbigen Ausgaben nur, wenn man Modelsim (den Simulator) von der Konsole aus startet, im interaktiven Betrieb werden die Escape-Sequenzen nicht interpretiert, und dann sieht das etwas komisch aus… Alle Ausgaben von Modelsim landen auch in der Datei transcript, wenn man diese Datei mit cat ausgibt sieht man auch die Farben. Wenn man die Datei mit less anschaut muss man dafür den Parameter -R angeben (also etwa less -R transcript), ansonsten „schützt“ einen less vor den Sequenzen.

Ein Gedanke zu „Schöne Debugausgaben mit VHDL“